Journal of Nanoelectronics and Optoelectronics

Vol. 12, pp. 1–13, 2017

www.aspbs.com/jno

## **ARTICLE**

# Novel 10-T Write Driver SRAM Design Using 45 nm CMOS Technology with Leakage Current Reduction Scheme for FPGA Routing Switch Architecture

S. Lakshmi Narayanan<sup>1,\*</sup>, Reeba Korah<sup>2</sup>, and A. Swarnalatha<sup>3</sup>

Bulk Complementary metal oxide semiconductor (CMOS) technology suffers from severe leakage power for gate lengths lesser than 45 nm. Static Random access memory (SRAMs) occupy a significant space in the memory architecture of system on chip (SOCs). To reduce the adverse effects of CMOS technology, SRAMs are implemented using FinFet technology. This research presents a new leakage reduction technique for SRAM cell implemented in FinFet technology. The proposed technique is a combined implementation of diode connected load transistors which operate only in saturation when turned on, to cutoff leakage current through access transistors and sleep transistors to control the flow of leakage current through the SRAM cell. The combined effect of these two types of transistors reduces leakage current in the range of nanoamperes. Moreover, the above stated technique when implemented in Fin Field Effect transistor (FinFet) SRAM structures becomes much suitable for memory architectures. Routing is an important step in Field programmable gate array (FPGA) design which is totally in view of how the interconnection is finished amid of the Configurable logic blocks (CLBs). In order to reduce the power consumption as well as power dissipation of the FPGA routing circuit, Different transistor styles of FinFet SRAM such as 6T and 10T structures are combined with Type-II write driver structure and it is simulated using Tanner (T-Spice) with 45 nm technology. Results show significant reduction in static current and power dissipation. With reasonable read/write stability in standby Type with a slight increase in area.

**Keywords:** FinFet Technology, Leakage Current, Stacking, Power Consumption, Diode Connected Load, SRAM, CMOS Integrated Circuits.

### 1. INTRODUCTION

Power consumption and energy saving has become the main factor of concern in emerging low power circuits. Alternate design decisions for low power consuming circuits have gained prominence in both logic level and storage level circuits. A storage circuit becomes active only when we read or write something in to it and ruins in standby Type and hence it is prone to significant amount of leakage current. It is quite interesting to observe

that consumer market demands minimal power consumption with maximal energy efficiency as well to retain longer battery hours. System on Chip (SOC) is the recent advancement in the integrated circuit technology market today. Technological advancements made things unimaginably possible and it is indeed interesting to note that a single chip comprises an entire system to perform certain operations. However, in a typical SOC 70% of the area is occupied by memory architectures. SRAMs are used as memory element in these architectures. To make an SOC affordable, the area, stability, reliability, leakage power consumption and performance of these SRAM architectures should be carefully crafted. With recent technological advancements in the range of nanometers, the size of the transistors got reduced where as the leakage current got shoot up exponentially. Various spillage lessening strategies are referred to in the writing with its own particular points of interest and impediments. When considering gate lengths <45 nm, CMOS technology shows significant

Email: lakshminarayanan574@gmail.com

Received: xx Xxxx xxxx Accepted: xx Xxxx xxxx

<sup>&</sup>lt;sup>1</sup>Research Scholar, Anna University, Chennai 600025, India

<sup>&</sup>lt;sup>2</sup>Alliance College of Engineering and Design, Alliance University, Bangalore 562106, India

<sup>&</sup>lt;sup>3</sup>St. Joseph's College of Engineering, Old Mahabalipuram Road, Semmencherry, Chennai 600119, India

<sup>\*</sup>Author to whom correspondence should be addressed.

drawbacks rather than its benefits. Hence the demand for alternate device technologies came in to existence. Several technologies were cited by researchers among which Fin-Fet served as an effective alternative. The main advantage of FinFet over other technologies is that it can be fabricated in the same foundry of bulk CMOS technology. This provides a significant cost reduction too. 12 At exhibit situation the spillage ebb and flow in Low power FPGA steering switch is dispersed in both the utilized and the unused piece of the FPGA. The prevalence of interconnect with the researchers to concentrate on FPGA control enhancement. In this section, The Type II based FPGA steering switches associated with FinFet SRAM which help to diminish control utilization of the directing switch too as static current and control defer product (PDP). 14–18

FinFet is a twofold entryway gadget where biasing for the two doors is done independently. It gives noteworthy area lessening, better execution time. The proposed procedure is actualized in Independent entryway Type FinFet SRAM cells and its execution is noted. Results demonstrate noteworthy spillage decrease. The association of the paper is as per the following. Section 2 depicts the traditional mass CMOS 6T SRAM cell and its operation, Section 3 examines the current spillage diminishment systems, Section 4 includes the vitality demonstrating in SRAM cluster engineering, segment 5 includes the FinFet based 6T SRAM cell and its operation, Section 6 talks about the proposed spillage decrease procedure, Section 7 clarifies the usage of proposed Type-II construct FinFet 10-T SRAM in light of FPGA steering switch architecture Section 8 includes the outcomes and Section 8 finishes up the paper.

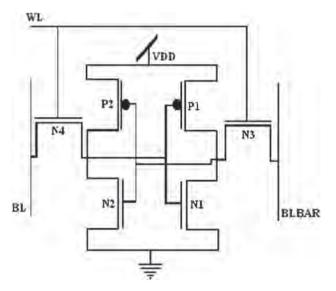

#### 2. CONVENTIONAL 6T SRAM DESIGN

A typical 6T SRAM cell has two inverters associated in a cross coupled manner. It acts as a bistable latch and stores a bit of information in the cell. It contains two pass transistors which provide access to the value stored in the cell. In addition to these, it consists of a wordline WL and two bitlines BL and BLBAR. WL is used to provide the required threshold value to the two access transistors and BL and BLBAR to read and write contents in the cell. The Present stores value in the cell is retained until the power is on.<sup>1</sup>

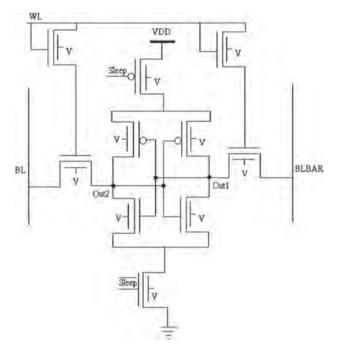

Types of Operation: SRAM operates in three Types, standby Type or hold Type, read Type and write Type. Standby Type: WL is made to low during standby Type this inturn cuts off the gate voltages and turns off the two access transistors. The value stored in the unit is retained by the two cross coupled inverters feeding each other. The value in the cell is retained as long as the power supply  $(V_{\rm DD})$  is high. A small amount of current flows through the cell which is nothing but the leakage current. Then the structure of conventional 6T SRAM design has been shown in Figure 1.

Fig. 1. Conventional 6T SRAM cell.

*Read Type*: During the read Type, the value stored in the cell can be read from it. To read the content that is stored in the cell, voltage at WL is turned high which in turn turns on the two access transistors. Both BL and BLBAR are precharged to  $V_{\rm DD}$ . The data stored in the cell, one of the bitline goes low (discharges to ground) and the difference value between the two bitlines are amplified by the sense amplifier circuitry and the output is read from the cell.

Write Type: This Type is used to write a new value in the cell. To perform a write operation, voltage at WL is turned high and this provides the required gate voltage to turn on the two access transistors. The value to be stored is

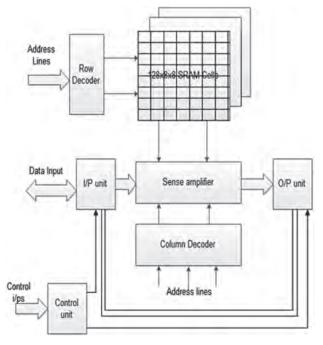

Fig. 2. SRAM array architecture.

applied to BL and its complement to BLBAR. When the latch changes its value the WL is turned off and the value is stored in the cell.

The above Types of operation occurs in a single cell. A typical memory architecture consists of an array of SRAM cells. The SRAM array architecture shown in Figure 2. It consists of a row decoder to choose the particular row to which the cell belongs and a column decoder to choose the particular column to which the cell belongs. The control and i/o circuitry provide the required control and data information required for the cell. The sense amplifier amplifies the data store in the cell and provides the yield.

## 3. LITERATURE SURVEY ON LEAKAGE REDUCTION TECHNIQUES

A few leakage decrease methods have been referred to in the writing. To decrease the measure of spillage current in a circuit it is important to diminish the supply voltage and edge voltage of the transistors. More finished, it is important to gauge the measure of leakage current in a circuit to actualize spillage decrease techniques.<sup>6</sup> In applications that require low to medium performance, operating transistors in the subthreshold region is gaining prominence. To operate a transistor in the subthreshold region device and circuit level optimization need to be performed. Longer channel length transistors are more efficient to operate in the subthreshold region.8 SRAM has gained significant importance in SOCs. Technology scaling has been very useful in implementing SRAM array architectures. In advanced technology nodes, such as gate lengths <65 nm scaling has become extremely difficult.9 In the UDSM range devices, power dissipton issues are quite challenging. International Technology Roadmap for Semiconductors projects a minimum power of 3 W for semiconductors in 2020. Hence the need for leakage reduction techniques is on the high.<sup>5</sup> A novel technique called INDEP is proposed to diminish the measure of leakage current and postponements in the circuit. Two transistors, namely a PMOS and a NMOS known as indep transistors are embedded between the draw up and pull down system of the circuit. The yield is gotten from the deplete of the two indep transistors associated together.<sup>13</sup> Another 9 transistor SRAM is actualized in 32 nm innovation with better execution and soundness with decreased process varieties. A parameter SPR is developed to indicate the figure of value of the proposed SRAM cell which demonstrates that the proposed SRAM is appropriate for thick nanometer SRAM designs. 10 A full chip leakage analysis framework for technology node beyond 65 nm is proposed. The method uses analytical Typels to capture the process variations. The method is able to handle both Gaussian and non Gaussian distributions and uses a quadratic logarithmic Typel for leakage analysis. The proposed method is tested in 65 nm chips and found to be very effective.<sup>3</sup> Leakage power has

turn out to be a significant problem in submicron range devices. The choice of leakage lessening technique turn out to be best when the circuit designer chooses it.<sup>2</sup> Bulk CMOS technology suffers from serious leakage issues. It is necessary to find a suitable leakage reduction technique in both circuit and architectural level to minimize power consumption.8 MPT8T is an efficient SRAM cell with pmos pass transistors. It provides significant improvement in read and write stability in 45 nm technology.<sup>7</sup> Memory architectures consume a significant amount of energy. MutiVth technique is very effective in reducing the overall energy consumption of SRAMs. SVL is an efficient dynamic self controllable voltage level change to decrease spillage control utilization in 7T SRAM cells.<sup>1</sup> SVL technique is effective in reducing leakage currents in standby Type when compared with other leakage reduction techniques.

## 4. ENERGY TYPELING OF SRAM ARRAY ARCHITECTURE

A critical design term in Ultra Deep sub micro meter (UDSM) technology devices is power/energy consumption. To reduce the amount of energy consumed, supply voltage is reduced to its minimum. An SOC consists of arrays of SRAM cells. Power consumed by an SRAM cell can be confidential as switching command/dynamic energy and leakage control/static energy. Hence, to determine the energy consumed by an SRAM, it is necessary to take into account its dimensions, switching energy and leakage power. To calculate the energy consumed by an SRAM cell, it is necessary to eliminate the array accessories like decoders, sense amplifiers, multiplexers, i/o circuitry etc.

The energy consumed by an SRAM array can be expressed as

$$E_{\rm T} = E_{\rm S} + E_{\rm L} \tag{1}$$

where  $E_{\rm T}$  is the total energy consumed,  $E_{\rm S}$  is the switching energy or dynamic energy and  $E_{\rm L}$  is the leakage energy or static energy. To analyse each of these components separately, we get

$$E_{S} = P_{\text{READ}}(C_{\text{READWL}} * V_{\text{DD}}^{2} + N * P_{0} * C_{\text{READBL}} * V_{\text{DD}}^{2})$$

$$+ P_{\text{WRITE}} \left( C_{\text{WRITEWL}} * V_{\text{DD}}^{2} + \frac{N}{M} * C_{\text{WRITEBL}} * V_{\text{DD}}^{2} \right)$$

$$(2)$$

where  $P_{\rm READ}$  is the probability of read occurrences,  $C_{\rm READWL}$  is the capacitance associated with read word line,  $V_{\rm DD}$  is the supply voltage applied,  $P_{\rm WRITE}$  is the probability of write operation,  $C_{\rm WRITEWL}$  is the capacitance associated with write wordline, N is the number of bitlines discharged during read operation and  $C_{\rm WRITEBL}$  denotes the write bitline capacitance. The read wordlines are shared and so multiple bitlines are discharged during read operation. N/M determines the switching capacitance for write

bitlines.  $P_0$  denotes the probability of reading a 0 bit and while reading a 1 bit no switching occurs. Hence the probability of switching is high when reading a 0.

The leakage energy,  $E_{\rm L}$  in an SRAM array is given by,

$$E_{\rm L} = V_{\rm DD} * I_{\rm L} * T$$

where,  $I_L$  is the current used due to leakage and T is the time period of computation.

$$E_{L} = V_{\text{DD}} * K * \left( I_{\text{SNMOS}} * e^{(\text{VGS-VTH}_{n})/(n\text{VT})} + I_{\text{SPMOS}} * e^{(\text{VGS-VTH}_{p})/(n\text{VT})} \right) * (1 - e^{-\text{VDS/VT}}) * T$$

(3)

where K signifies the aggregate number of SRAM cells in the exhibit, the  $I_{\rm SNMOS}$  and  $I_{\rm SPMOS}$  indicate the scaling parameters for NMOS and PMOS gadgets separately, VGS and VDS mean the door to source voltage and deplete to source voltage individually. VT is the warm voltage and VTH $_n$  and VTH $_p$  indicate the limit voltage for NMOS and PMOS gadgets separately.

## 5. DESIGN OF FINFET BASED SRAM CELL CIRCUIT

FINFET is a double gate device with self alignment for both the gates and the fabrication technology is compatible with that of CMOS technology. FINFET based SRAM designs is more efficient in the design of memory architectures for SOCs. The applied voltage, threshold voltage and fin height are adjusted to improve performance, stability and reduce leakage current. It is to be noted that increasing the height of the fin reduces the supply voltage  $(V_{\rm DD})$  but it creates issues pertaining to stability. FINFET based SRAM cell offers better performance, higher stability, lower  $V_{\rm DD}$ , better scaling and reduced short channel effects. FINFET operates in four Types, namely shorted gate Type, independent gate Type, low power Type and hybrid Type.

Shorted Gate Type [SG]: Shorted gate Type operation is otherwise called tied entryway Type. In this method of operation, both the front door and back entryway are entwined and the gadget goes about as a regular CMOS SRAM with decreased short channel impacts. The outline choice for SRAM is like that of the ordinary CMOS SRAM plan.

Independent Gate Type [IG]: In independent gate Type, separate bias voltages are applied to both gates of the FIN-FET transistor and the threshold voltage can be adjusted accordingly. The operation of FINFET SRAMs is similar to that of CMOS SRAM. The height of fin is minimum and the transistors used are also of minimum size. As both the gates are biased independently, the leakage reduction and performance is significantly higher than the other Types of operation.

Low Power Type [LP]: In low power Type, a voltage superior than  $V_{\rm DD}$  is connected to the back door of the PMOS transistor and electrical energy lower than GND is connected to the back entryway of a NMOS transistor. Half and Half Type: Hybrid Type is a mix of IG and LP Type. Appropriate decision of gadget must be finished by the creator as per the outline necessity. As independent gate Type tops among the four, it is used in the proposed SRAM design.

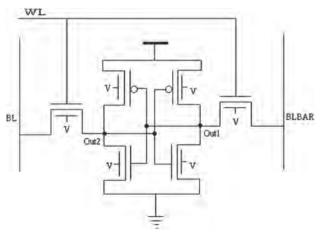

## 6. INDEPENDENT GATE TYPE FINFET SRAM CELL STRUCTURE

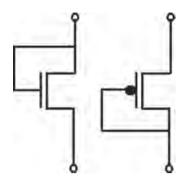

Leakage current is a critical factor in both CMOS and Fin-Fet based SRAM cell designs. Independent Gate Type 6T FINFET SRAM cell has been shown in Figure 3. A number of nanometer range designs are subject to this issue. In a typical SRAM cell, a significant amount of leakage current flows both through the cell and the access transistors. An efficient method to decrease the stream of spillage current is to build the resistance of the way through which the spillage current streams. Some of the time, it winds up plainly hard to locate a solid resistance of a specific sort. In such cases, a Metal oxide semiconductor (MOS) transistor can be made to go about as an efficient small signal resistor by shorting its gate and drain together. These transistors are known as diode connected transistors. These transistors operate only in saturation region when they are turned on and remains in off state for any minor current flow. Both PMOS and NMOS transistors can be made to act as diode connected transistors. The diode connected transistor has been shown in Figure 4. In this design, we use NMOS diode connected transistors to cut off leakage current through the access transistors to its minimum. To minimize the leakage current through the cell standby Type, two sleep transistors are introduced, one above and the other below the cell. When a sense high electrical energy is apply to the sleep transistor, it turns off and

Fig. 3. Independent gate type 6T FINFET SRAM cell.

Fig. 4. Diode connected transistors.

Fig. 5. Independent gate type FINFET SRAM cell with diode connected transistors and sleep transistors.

offering a high resistance to block the flow of current in to the cell. Hence the flow of leakage current through the cell is minimized. Similarly, a low voltage is applied to the NMOS sleep transistor, which inturn turns off the NMOS transistor providing a strong resistance to minimize the discharge of leakage current to ground. When these two techniques are combined together, a steady drop in leakage current is obtained. The Independent Gate Type FINFET SRAM cell with diode connected transistors and sleep transistors shown in Figure 5.

## 7. PROPOSED METHOD WITH 10-T SRAM WRITE DRIVER CIRCUIT ON FPGA ROUTING DESIGN

The flow in Low power FPGA directing switch is dispersed in both the utilized and the unused piece of the

| Table I. Working | ng of type-I in various re | gions.                  |

|------------------|----------------------------|-------------------------|

| Sleepy type      | Drowse type                | Working                 |

| One              | Unknown                    | Actively (ON condition) |

| Zero             | Zero                       | Sleepy type             |

| Zero             | One                        | Drowse type             |

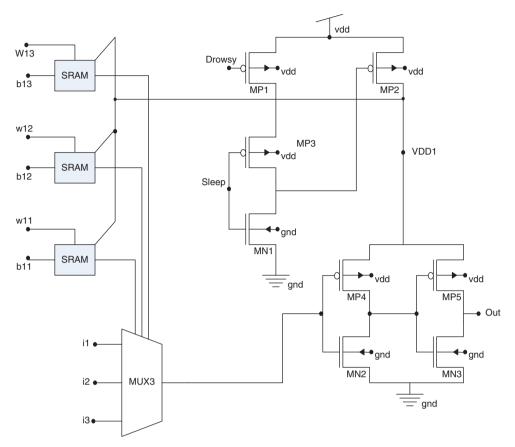

FPGA. The transcendence of interconnect through and through influenced the specialists to concentrate on FPGA to control optimization. Here, we display two methods Type-1 and Type II based FPGA steering changes which help to decrease control utilization of the steering switch however if there should be an occurrence of spillage control, it is around square with. This Existing plan took a shot at three unique Types: dynamic or rapid Type, low power Type and rest Type. Where as in our proposed outline we picked dynamic or fast Type, rest Type and sluggish Type shown in Table I.

As per the Table I in drowsy Type due to low voltage swing the power consumption which occurs at  $V_{\rm DD1}$  is more, which makes us to opt for Type-II design to optimize the power consumption of the FPGA routing switch. The transistor count in the Type-II (4-Transistors) is much less than Type-I (7-Transistors) which helps to reduce the power consumption of the design as well in order to overcome the drawback of low voltage swing which occurs in drowsy Type we are neglecting drowsy Type in Type-II design as shown in the Figure 6.<sup>19-21</sup> In Type-II during active Type, when sleep = 1 irrespective of drowsy state 0 or 1, makes the transistor MN1 = ON which pass the weak signal '0' as a gate input to MP2 transistor (MP2 = ON). Due to this above condition the supply voltage  $V_{\rm DD}$ is passed to logic circuitry and FIN FET SRAM via MP2 and other transistors are in idle state since drowsy state is 0 or 1. The supply voltage is analyzed at the node  $V_{\rm DD1}$  as shown in the Figure 6. Hence the supply voltage (1.8 V) is occurred at the node  $V_{\rm DD1}$  which helps to reduce the voltage fluctuation.

During Sleep Type, as observed from the Table II, the node sleep = 0 and drowsy = 0. At this condition when drowsy = 0, it makes the transistors MP1 = ON.

Further the node Sleep = 0 makes the transistor MP3 = ON and the source voltage supply for the MP3 is pass through the drain of the MP1. The gate input to the MP2 is acquired through the drain of the MP3 transistor and due to strong signal '1' which makes the MP2 transistor turns OFF, at this condition there is no voltage at  $V_{\rm DD1}$  to the logic circuitry and FINFET SRAM. Hence this said to be sleep Type condition. FINFET SRAM with compose driver hardware empowers the charging and releasing of the bit line. Compose driver is used for the assessment of the bit lines before read operations are completed.

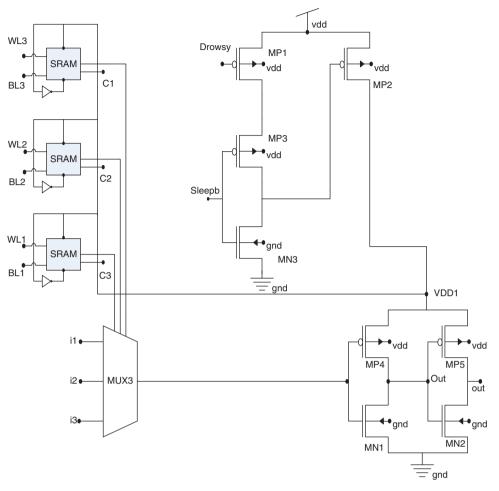

In 10T SRAM FINFET circuit one can guarantee that both the bit lines are charged to similar voltages previously

Fig. 6. Representation of type-II based FPGA routing switch plan.

perusing. In this area we might handle the issue of diminishing force utilization of compose driver hardware, to be specific, the word line drivers and word line hardware. The peruser ought to perceive that the compose driver, while being expansive, on account of the requirement for driving long, vigorously stacked word lines, adds to the general energy to a little degree, since at most one of the drivers is actuated at once rather than control lessening methods depicted beforehand, which endeavor to decrease voltage, compose circuits regularly have Supply voltages controlled by different variables. At the end of the day, the word line voltages utilized is dictated by the center, while the decoders work at Supply voltages required by encompassing rationale. Word line drivers are generally basic supports intended to fit in the column pitch of a memory cell little open door for control streamlining is accessible in these circuits. When in doubt, we would slant toward push meaning be as snappy as could be normal the situation being what it is, since it clearly impacts get the

Table II. Working of type-II in various regions.

Sleep Drowsy Function

One Unknown Actively (ON condition)

Zero Zero Sleepy type

chance to time for a FINFET SRAM. The different strides associated with composing, perusing and hold operations in the new circuit are proposed. In both the regular 6T FINFET SRAM and the proposed 10T FINFET SRAM with compose driver, the information which must be composed is first acquired with its supplement utilizing two reversing cradles. The information and its supplement is connected to BL circuits which independently deliver, supplemented yields just when compose empower flag "WL" is dynamic. This guarantees by empowering the compose Type, where the date goes to bit lines. The signs got from the altering cradle circuits are spoken to by PMOSFET (MP5) deplete.

Amid compose operation through the vitality recuperation driver, the information "BL" go to the bit lines is like the regular technique. In the event that if input flag "BL" is low, the capacitance of the bit line charges to the pinnacle voltage through diode P-sort Metal oxide semiconductor field impact transistor (PMOSFET) (MP5). However the most extreme voltage of the bit lines is restricted by the drop over the PMOSFET (MP5) switch. On the off chance that the information flag BL is high, the bit line capacitance N-sort Metal oxide semiconductor field impact transistor NMOSFET (MN6) releases to the assessment through NMOSFET (MN6). The complimentary move makes put in the other

Fig. 7. Representation of 10T FINFET SRAM with write driver circuit on type-II.

piece line 'BL b.' The information on the bit lines are passed to the FINFET SRAM by the entrance transistors. A large portion of the vitality from the bit line connected to the capacity hub which undergoes '1' to "0" change gets once again into the assessment through the Write recuperation driver (MP4, MP5, MN5, MN6) and inverters.

Compose operation implies store information into the hub (association between two cross coupled inverters MP2, MP3, MN2 and MN3) of FINFET SRAM cell. So as to store rationale "1" to the phone, BL is charged to  $V_{\rm DD}$  and BLB is charged to ground and tight clamp verse for putting away rationale "0". At that point the word line voltage is changed to  $V_{\rm DD}$  to turn "on" the NMOS (MN4) get to transistors. At the point when the entrance transistors are turned on, the estimations of the bitlines are built into B and BLB.

Amid read operation implies information read from the FINFET SRAM cell. To peruse from the cell the bitlines are charged to ground rather than  $V_{\rm DD}$  and the wordline voltage is set to  $V_{\rm DD}$  to turn on the NMOS (MN4) get to transistors. The hub (association between two cross coupled inverters MP2, MP3, MN2 and MN3)

with rationale "1" put away will pull the voltage on the comparing bitline up to a high (not  $V_{\rm DD}$  due to the voltage drop over the NMOS-MN6 get to transistor) voltage level. The other bitline is pulled to ground. On the off chance that the phone was putting away rationale "0" the voltage level of BL will be lower than BLB will yield rationale "0". On the off chance that the phone was putting away rationale "1" at that point the voltage level of BL will be higher than BLB then the sense speaker will yield rationale "1" (FarshadMoradi et al. 2011).

Thus the proposed 10T Write driver FINFET SRAM Type-II based FPGA steering switch cell structure outflanks amid compose operation which makes the static power much diminished than the 10T FINFET SRAM Type-II FPGA directing switch and the coordination of 10T Write driver FINFET SRAM Type-II based FPGA steering switch is appeared in the Figure 7.

#### 8. SIMULATION REPORTS

The simulation of 6T FinFet SRAM cell with execution of the projected work is finished in HSpice toolin 45 nm

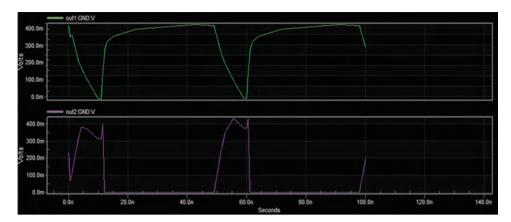

Fig. 8. Read and write waveforms of independent gate SRAM with the proposed technique.

expertise. The Typelling parameters of FINFET at 45 nm are as follows:

| Parameter                             | Value                  |

|---------------------------------------|------------------------|

| Length of the channel                 | 45 nm                  |

| Thickness of oxide                    | 1.5 nm                 |

| Si thickness                          | 8.4 nm                 |

| NMOS voltage level of front gate      | 0.33 V                 |

| NMOS voltage level of front back gate | 0.33 V                 |

| PMOS voltage level of front gate      | -0.23  V               |

| Threshold voltage of PMOS front gate  | -0.23  V               |

| Channel doping                        | $2e16 \text{ cm}^{-3}$ |

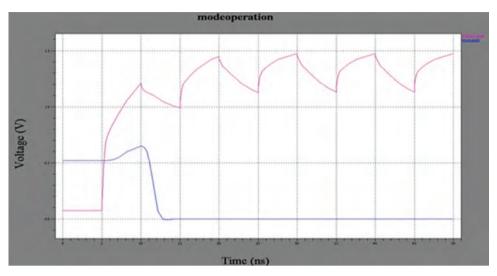

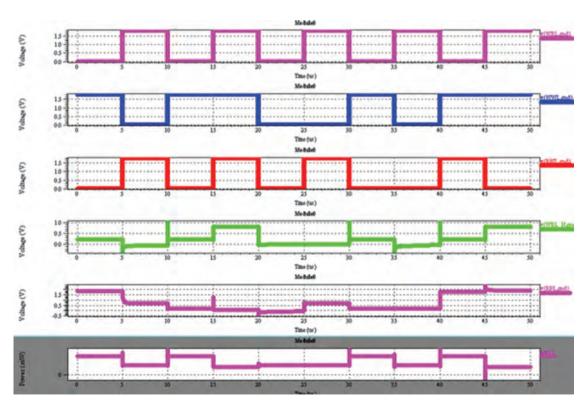

It is known that the outputs of the SRAM cell out1 and out2 are complement to each other. The read and write waveforms of the projected SRAM cell is as made known in Figure 8. The waveforms show significant stability during standby Type. In the proposed technique a Independent Gate Type of FinFet was used because the average power consumption of various Types of FinFet and Bulk Mosfet are simulated using SPICE Tool it will ensures the independent Gate Type is effective method in terms of reduced power consumption, read and write stability. The average power consumption of independent Gate Type FinFet and Bulk Mosfets are shown in Table III. The conventional 6T independent gate Type FINFET SRAM cell is simulated and its leakage power and leakage current is found as 28.64 nW and 135.24 pA. To reduce the leakage current further, simulations are done by implementing the proposed technique in the 6T SRAM cell in

**Table III.** Simulation results of various types of FinFet at 45 nm technology.

| Sl. no | Technology (nm) | Methodology    | Average power (watts) |

|--------|-----------------|----------------|-----------------------|

| 1      | 45              | Bulk MOSFET    | 2.47E-07              |

| 2      | 45              | FinFet SG type | 3.46E-06              |

| 3      | 45              | FinFet LP type | 2.29E-06              |

| 4      | 45              | FinFet IG type | 4.58E-07              |

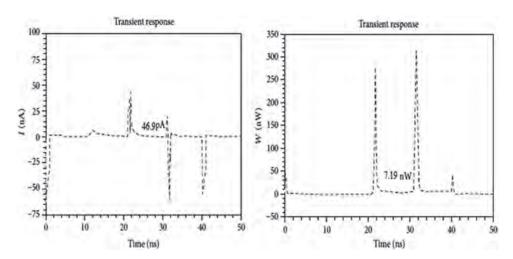

independent Type. The leakage power and leakage current reduces to 7.19 nW and 46.9 pA respectively as shown in the Figure 9. Table IV shows the parameters like a leakage current in subthreshold regime, leakage power, and power consumption using independent-gate SRAM FinFet with diode connected transistor and sleep transistor. Figure 10 shows the leakage power and leakage current for transient analysis done with the proposed technique applied in Independent gate Type operation of FinFet for 0 to 50 ns.

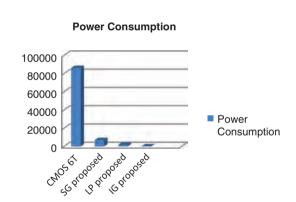

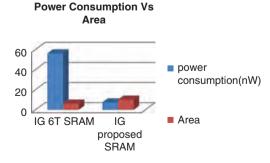

Figure 11 shows the power consumption of the conventional 6T FinFet SRAM cell in independent gate Type operation with out any leakage reduction techniques and the FinFet SRAMs by applying the proposed technique in shorted gate, low power and independent gate Type of operation. It is found that independent gate Type consumes the lowest power. Figure 11 shows the difference in power consumption between the conventional 6T SRAM in IG Type and SRAM with the proposed technique in IG Type of operation. It is clearly T evident that the proposed technique consumes significantly lesser amount of power than the conventional 6T SRAM in IG Type. When comparing area, the proposed technique has a slight area overhead when compared with the conventional 6T SRAM.

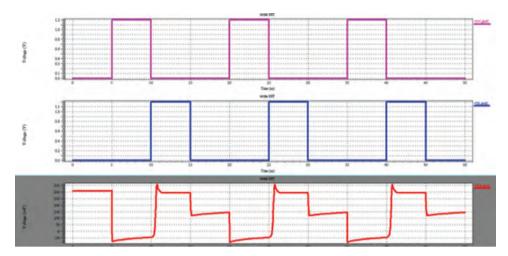

Further for the implementation of The conventional 6T and 10T Fin Fet SRAM cell structures are actualized in standard 45 nm CMOS innovation.<sup>22,23</sup> Both the cells have the indistinguishable information line drivers. Yet, if there should be an occurrence of 10-T Fin Fet SRAM cell the compose Type is controlled by compose hardware which lessens the exchanging action of the transistor. Mimicked Read/Write Type of operations and the proposed strategy execution of the cell is assessed. Since at most one of the drivers is enacted at once instead of energy lessening systems portrayed beforehand, which endeavor to diminish voltage. Compose circuits frequently have Supply voltages controlled by different variables. At the end of the day, the word line voltages utilized is controlled by the center, while the compose driver works at supply Voltages required by encompassing rationale. The 6T Fin Fet SRAM based Type-II plan static power

Fig. 9. Leakage current and leakage power consumption of the proposed technique.

scattering is substantially higher than the new outline. The proposed configuration compose static power dissemination is diminished up to by bringing down the exchanging 10% action and in addition circuit way deferral of the transistor when contrasted with existing 6-T Fin Fet SRAM based Type-II FPGA Routing switches. As appeared in the Figure 12.

As the compose hardware decreases the undesirable the exchanging movement of the transistors and also circuit way delay in 10T SRAM based Sort II plan with compose driver makes the proposed strategy has a processable power diminishment in the SRAM cell structure. This guarantees the power dispersal is never again a bottleneck plan amid compose operation. As appeared in the Figures 13 and 14 On the BL side, the draw up transistor bit line toward  $V_{DD}$ , a coherent 1. On the off chance that the substance of the memory was a 0, the inverse would happen and BL would be pulled toward 1 and BL toward 0. At that point these BL and BL will have a little distinction of delta amongst them and after that these lines achieve a sense speaker, which will detect the higher voltage line and in this way will tell whether there was 1 put away or 0. BL input-drivers are intended to diminish the exchanging exercises of the past condition of the cross-coupled inverters and recreation of

Table IV. Leakage current, leakage power and average power consumption of various techniques.

| Sl. | Technique             | Leakage<br>current<br>(pA) | Leakage<br>power<br>(nW) | Average power consumption (nW) |

|-----|-----------------------|----------------------------|--------------------------|--------------------------------|

| 1   | IG FinFet             | 135                        | 28.64                    | 65                             |

| 2   | IG FinFet with HT     | 72                         | 24.50                    | 42.6                           |

|     | NMOS stacking         |                            |                          |                                |

| 3   | IG FinFet with HT     | 71                         | 18.20                    | 38.50                          |

|     | NMOS sleep transistor |                            |                          |                                |

| 4   | IG FinFet with diode  | 46.9                       | 7.19                     | 35.62                          |

|     | connected transistor  |                            |                          |                                |

|     | and sleep transistor  |                            |                          |                                |

the last coordination is appeared in Figure 15 and the static power is diminished by lessening the exchanging movement of the transistors, which thusly decreases the entryway tally. The compose driver plays out an information WL and BL on a cell that at first contains a '0', yields were gotten for ordinary working conditions, read cycle is begun by pre-charging both the bit lines to a sensible 1, at that point stating the word line WL, empowering both the entrance transistors. The second step happens when the qualities put away in Balance Fet SRAM exchanged to

Fig. 10. Power consumption of conventional bulk CMOS SRAM FIN-FET SRAMs with the proposed technique in various types.

Fig. 11. Power consumption of IG 6T SRAM and IG SRAM with the proposed technique versus area.

Fig. 12. 6T SRAM cell results with type-II operation.

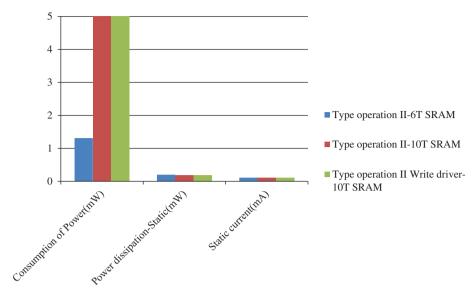

the bit lines by leaving BL at its pre-charged esteem and releasing BLB. The power utilization is 640 mW, static power dispersal is 0.18 mW, static ebb and flow is 0.1001, PDP is 1.0809 and EDP is 6.48 zW/s As watched shape the Table V the power utilization in 10T compose driver Sort II based FPGA directing switch is because of higher transistors check. The 15 transistors expanded in memory bank of the proposed strategy when contrast with Sort operation II with 10T Balance Fet SRAM. The abatement in static

power dispersal of the proposed strategy by diminishing the exchanging action of the cross couple inverters in view of information inputs (BL). Advance this declines the circuit way postpone which thus diminishes the PDP and Vitality defer product (EDP) of the proposed technique.

#### 8.1. Cell Spillage

Amid the standby Sort of the transistor, static spillage current is the essential parameter for SRAM cell of the

Fig. 13. Model outcome of type-II operation on FPGA routing structure with 10T Fin Fet SRAM cell with.

Fig. 14. Model outcome for write driver type II operation of 10T Fin Fet SRAM cell.

Fig. 15. Outcome of 10T Fin Fet SRAM cell with write driver type II operation—simulation results.

directing switch design of FPGA. Despite the fact that the proposed 10T based Sort II outline with compose driver has extra transistor tally, our oath line assessment voltage of 1.8 V shows less spillage momentum of the SRAM cell i.e., 10% lessening. Moreover, the draw down transistors are less critical than those in the current SRAM cell, demonstrates less spillage current.

In PDP, if D speaks to defer and P speaks to control utilization of the circuit, at that point the metric can be communicated as PDP (vitality) = Power  $(P) \times \text{Delay } D$ ). The EDP (Vitality Postpone Item) can be assessed by

**Table V.** Summing up of results of conventional and proposed structure.

| Parameter                | * 1 1      | Type operation II with 10T Fin Fet SRAM | Type operation II<br>write driver 10T<br>Fin Fet SRAM |

|--------------------------|------------|-----------------------------------------|-------------------------------------------------------|

| Power consumption        | 1.41 mW    | 14.96 mW                                | 610 mW                                                |

| Static power dissipation | 0.20 mW    | 0.17 mW                                 | 0.14 mW                                               |

| Static current           | 0.116 mA   | 0.105 mA                                | 0.108 mA                                              |

| PDP                      | 1.66 pW/s  | 130 pW/s                                | 1.0809 pW/s                                           |

| EDP                      | 4.646 zW/s | 855 zW/s                                | 5.48 zW/s                                             |

Fig. 16. Proportional study of optimized parameters.

increasing Vitality with normal *D*. On the off chance that power is higher need then both EDP and PDP frameworks may not give better arrangements. The power varieties of the SRAM are considered in detail as appeared in Figure 16.

A novel 10T FinFet SRAM based Sort II with compose driver hardware is proposed and broke down. The read and compose operations of the FinFet SRAM cell structure have control scattering misfortune amid the compose cycle, which is controlled by composing driver hardware. As a result, static power dispersal is diminished 10% than that of the 6T Balance Fet SRAM and 10T FinFet SRAM based Sort II outline FPGA directing plan. In examination, it is closed the new outline a reasonable decision for low power steering switch in top of the line FPGA's.

### 9. CONCLUSION

SRAMs involve >70% of the region in a run of the mill SOC. Subsequently its energy utilization and spillage power ought to be limited to the most extreme inorder to enhance its execution. From the above outcomes, it is obviously clear that the proposed strategy devours around 95% lesser measure of energy utilization with much lessening in spillage control utilization. The proposed strategy is much reasonable for memory structures and implanted framework outlines. Various spillage lessening procedures have been referred to in the writing with its own benefits and bad marks. The proposed procedure with its leeway of diminished power utilization has a blemish of slight increment in region which ought to be taken in thought while planning. In examination of 10T FinFet SRAM based Sort II outline FPGA steering design, it is closed the new plan an appropriate decision for low power directing switch in top of the line FPGA's.

#### **References and Notes**

- B. Wang, J. Zhoa, and T. T. H. Kim, *Microelectron. J.* 46, 265 (2015).

- M. Geetha Priya, K. Baskaran, and D. Krishnaveni, Procedia Engineering 30, 1163 (2012).

- J. Xue, T. Li, Z. Yu, and Y. Deng, Integration, the VLSI Journal 43, 353 (2010).

- Masoud Rostami and Kartik Mohanram, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 30, 331 (2011).

- 5. N. Ekekwe and R. E. Cummings, Microelectron. J. 37, 851 (2006).

- P. F. Butzen, J. L. S. da Rosa, E. J. D. C. Filho, and A. I. Reis, *Microelectron. J.* 41, 247 (2010).

- Priya Gupta, Anu Gupta, and Abhijit Asati, International Journal of Reconfigurable Computing 2015, Article ID 749816 (2015).

- Ramesh Vaddi, S. Dasgupta, and R. P. Agarwal, VLSI Design 2009, Article ID 283702 (2009).

- V. Sharma, F. Catthoor, and W. Dehaene, SRAM Cell Bit Optimization (2013), Vol. XII, p. 172, ISBN: 978-1-4614-4038-3, www.springer.com.

- 10. S. Lin, Y.-B. Kim, and F. Lombardi, Integration, the VLSI Journal 43, 176 (2010).

- 11. Shyam Akashe and Sanjay Sharma, Wireless PersCommun. Journal 71, 123 (2012).

- Vandna Sikarwar, Saurabh Khandelwal, and Shyam Akashe, Chinese Journal of Engineering 2013, Article ID 738358 (2013).

- Vijay Kumar Sharma, Manisha Pattanaik, and Balwainder Raj, Microelectronics Reliability 54, 90 (2014).

- 14. K. Zhang, U. Bhattacharya, Z. Chen, F. Hamzaoglu, D. Murray, N. Vallepalli, Y. Wang, B. Zheng, and M. Bohr, SRAM design on 65 nm CMOS technology with integrated leakage reduction scheme, *IEEE Symp. VLSI Circuits Dig.* (2004), pp. 294–295.

- 15. F. Hamzaoglu, K. Zhang, Y. Wang, H. J. Ann, U. Bhattacharya, Z. Chen, Y. Ng, A. Pavlov, K. Smits, and Bohr, A 153 MB-SRAM design with dynamic stability enhancement and leakage reduction in 45 nm high-k metal-gate CMOS technology, IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers (2008), pp. 376–621.

- **16.** Y. Takeyama, H. Otake, O. Hirabayashi, K. Kushida, and Otsuka, A low leakage SRAM macro with replica cell

- biasing scheme, IEEE Symp. VLSI Circuits Dig. (2005), pp. 166–167.

- J. Wang and B. H. Calhouns, Canary replica feedback for near-DRV standby V<sub>DD</sub> scaling in a 90 nm SRAM, *Proc. IEEE Custom Integrated Circuits Conf.* (2007), pp. 29–32.

- **18.** A. Singhee and Rutenbar, Statistical blockade: A novel method for very fast montecarlo simulation of rare circuit events, and its application (**2007**).

- X. Tang, P. E. Gaillardon, and De Micheli, A study on buffer distribution for RRAM-based FPGA routing structures circuits and systems (LASCAS), 2015 IEEE 6th Latin American Symposium (2014), pp. 1–4.

- 20. R. Kanj, R. Joshi, and Nassif, Mixture importance sampling and its application to the analysis of SRAM designs in the

- presence of rare failure events, *Design Automation Conf.*, ACM, San Francisco, CA (2006), pp. 69–72.

- **21.** L. Dolecek, M. Qazi, D. Shah, and Chandrakasan, Breaking the simulation barrier: SRAM evaluation through norm minimization, *IEEE/ACM Int. Conf. Computer-Aided Design* (**2008**), pp. 322–329.

- 22. M. Qazi, M. Tikekar, L. Dolecek, D. Shah, and Chandrakasan, Loop flattening and spherical sampling: Highly efficient typel reduction techniques for SRAM yield analysis, Design Automation and Test in Europe, March (2010), pp. 801–806.

- 23. K. J. Antreich and Graeb, Circuit optimization drive by worst-case distances, *IEEE/ACM Int. Conf. Computer-Aided Design* (2008), pp. 166–169.